Timing Dasar Memory

Pasti masih pada bingungkan dengan namanya timing Memory, angka angka apa aja sih yang terdapat dalam memory. Semua itu ada Fungsinya. yang menentukan kinerja dari sebuah dari RAM. Berikut penjelasan singkat dari Timing memory;

CAS Latency (tCL) Timing

CAS Latency adalah : adalah jeda / delay pada proses siklus CAS (Column Address Strobe) atau biasa juga disebut Column Address Select yaitu sebuah kontrol yang mengatur terhadap banyaknya waktu yang diperlukan dalam sebuah siklus (cycle) untuk mengirim perintah membaca dan mengeksekusinya. Sedangkan latency adalah jeda antara proses dari awal CAS hingga akhir CAS. Jadi semakin cepat sebuah siklus CAS ini berakhir berarti data yang bisa diproses juga semakin cepat selesai dan hal ini akan meningkatkan performa memori dan system secara keseluruhan.

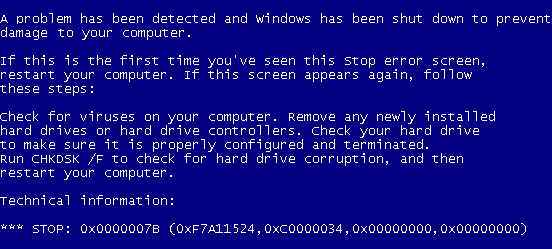

contoh : 5-5-5-15 Angka “4” (Warna merah) adalah CAS timing. ( Liat gambar diatas)

tRCD Timing

tRCD singkatan dari RAS to CAS Delay (Row Address Strobe/Select to Column Address Strobe/Select). Merupakan prosess untuk memberikan satu perintah aktif (active command) dan perintah baca/tulis (read/write commands). Sedangkan tRCD merupakan waktu yang dibutuhkan pada satu siklus RAS to CAS tersebut

contoh :5-5-5-15 Angka “5” (Warna merah) merupakan tRCD timing.

tRP Timing

merupakan singkatan dari Row Precharge Time yaitu waktu minimum antara perintah aktif (active command) dan perintah baca/tulis (read and write command) pada bank selanjutnya dari modul memori.

contoh :5-5-5-15 Angka “5” (Warna merah) adalah tRP timing.

tRAS Timing

tRAS adalah sebuah angka putaran clock yang diambil berdasarkan perintah aktif dari setiap bank memori dan memberikan precharge sebelum dinonaktifkan.

RAS Active Time adalah banyaknya waktu yang diperlukan sebuah baris diaktifkan lewat precharge command dan selanjutnya dinonaktifkan. Sebuah baris tidak dapat dinonaktifkan sebelum tRAS selesai. Semakin rendah tRAS, semakin cepat performa memori, tetapi jika diset terlalu rendah, akan menyebabkan adanya data yang terpotong (data corruption) karena menonaktifkan baris terlalu cepat sebelum proses RAS selesai.

Ada rumus umum dalam penentuan tRAS yaitu sebagai berikut :

tRAS = tCL + tRCD + tRP (+/- 1) rumus ini menggambarkan bahwa dibutuhkan waktu yang tepat sebelum menutup bank memori.

Terlihat bahwa semua main timing (CL, tRCD, tRD) memberikan andil terhadap penentuan tRAS

contoh :5-5-5-15 Angka “15” (Warna merah) adalah tRAS timing.

(Angka 5-5-5-15 hanyalah contoh dari timing memory dasar utama)

Dari contoh diatas terdapat 4 (empat) timing yang terdapat dalam sebuah modul memori. Urutannya adalah CAS-tRCD-tRP-tRAS. Semakin rendah timing ini, semakin tinggi performa dari sebuah modul memory, namun juga akan menimbulkan instability pada sistem apabila diset terlalu rendah (ketat).

Beberapa merek dan seri memori tertentu yang pada umumnya memiliki harga lebih tinggi dibanding rata-rata RAM, dapat diset pada timing yang jauh lebih rendah (istilah umumnya : ketat “tight”) ataupun pada speed (baca : frekuensi) yang tinggi. Timing dan frekuensi tersebut dapat diset langsung dari motherboards maupun dengan menggunakan software 3rd party under windows seperti : memset, CBID (Central Brain Indentifier), AOD (AMD Overdrive), setfsb, clockgen dan lain-lain.

Namun demikian, settingan lengkap pada memory tidak akan ditemui pada semua board. Hanya board-board khusus untuk kalangan enthusiast saja yang memiliki opsi yang sangat detil untuk pengoptimalan timing memori.

Timing RAM yang lain (biasa disebut alpha timing) merupakan timing yang hanya bisa ditemukan pada board-board yang khusus untuk overclocking. Berikut beberapa timing alpha yang umum ditemukan :

- Command Rate: Istilah lainnya adalah CPC (Command Per Clock). Yaitu jumlah waktu dalam satu siklus pada saat penentuan pemilihan chip dan perintah dapat dijalankan. Semakin rendah Command Rate (misal : 1T) maka performa akan lebih meningkat namun instability pada system akan semakin besar, Oleh sebab itu 2T is digunakan untuk menjaga stabilitas sistem.

- tRC Timing: Row Cycle Time. adalah waktu terpendek dalam sebuah siklus dalam sebuah baris untuk menyelesaikan sebuah siklus penuh. Pada umumnya bisa dicari dengan menjumlahkan antara tRAS dan tRP (rumus : tRC = tRAS + tRP). Kalau diset terlalu pendek akan menyebabkan data corrupt sedangkan kalo terset terlalu longgar (tinggi) akan menyebabkan penurunan performa dan peningkatan stability.

- tRRD Timing: Row to Row Delay or RAS to RAS Delay. Adalah jumlah siklus yang dibutuhkan untuk mengaktifkan bank memory selanjutnya. tRRD merupakan lawan dari tRAS. Semakin ketat timing akan semakin meningkatkan performa, tapi akan menyebabkan instability.

- tRFC Timing: Row Refresh Cycle Timing. Merupakan jumlah siklus untuk merefresh sebuah baris dalam sebuah memory bank. Kalo value ini diset terlalu rendah dapat menyebabkan data corruption, dan bila diset terlalu tinggi akan menyebabkan penurunan performa, tetapi akan meningkatkan stability.

- tRW Timing: Write Recovery Time. Adalah jumlah siklus yang dibutuhkan setelah proses precharge dan proses penulisan valid. Value ini untuk memastikan data telah ditulis dengan tepat.

- tRTW/tRWT Timing: Read to Write Delay. Pada saat perintah penulisan diterima, nilai ini menentukan besarnya siklus yang diperlukan untuk menjalankan perintah tersebut.

- tWTR Timing: Write to Read Delay. Yaitu jumlah siklus yang diperlukan antara perintah penulisan yang valid (valid write command) dan perintah penulisan selanjutnya. Semakin rendah ajan meningkatkan performa namun dapat menyebabkan instability.

- tREF Timing: Waktu yang diperlukan sebelum content direfreshed sehingga tidak akan kehilangan data dan bisa menyebabkan corrupt. Dihitung dalam satuan micro-seconds (µsec).

Timing-timing tersebut di atas sering disebut sebagai timing alfa, dan jarang ditemukan pada board-board kelas lowend atau board yang tidak difungsikan sebagai board overclocker. Namun demikian tidak perlu khawatir karena dengan menggunakan program memset for windows semua opsi di atas bisa diakses langsung dari windows. Untuk mendapatkan program memset bisa didownload disini

0 Comments